글 / 미조우 미쉘 탄(Mizhou (Michelle) Tan) RF 제품 애플리케이션 엔지니어, 아나로그디바이스(Analog Devices, Inc.)

이 글에서는 주파수 호핑(FH)의 기본 개념, 아나로그디바이스 ADRV9002 SDR(software-defined radio) 송수신기의 유연한 PLL 아키텍처를 활용한 FH 설계 원리, 그리고 이 디바이스가 제공하는 4가지 주요 FH 기능에 대해서 설명한다.

이들 기능을 사용하면 Link 16 같은 애플리케이션에서 FH를 유연하게 구현하고, 단일 및 듀얼 채널 동작 모드로 빠르게 실시간으로 캐리어 주파수 로딩을 할 수 있다. 뿐만 아니라 이 SDR 송수신기는 FH와 멀티칩 동기화(MCS) 및 디지털 전치왜곡(DPD)의 조합을 통해 오늘날의 복잡한 통신 시스템에서 보다 향상된 성능을 달성하는 매력적인 솔루션을 제공한다.

.jpg)

머리말

주파수 호핑(FH)이란 통상적인 무선 통신과 다르게 캐리어 주파수를 빠르게 바꿔가면서 무선 신호를 전송하는 기법으로서1, 니콜라 테슬라(Nikola Tesla)가 1903년에 자신의 미국 특허 ‘시그널링 기법(Method of signaling)’에서 처음으로 언급했다. 그러다 1942년에 여배우인 헤디 라마르(Hedy Lamarr)와 작곡가인 조지 앤틸(George Antheil)이 무선으로 어뢰를 제어하는 것에 대한 간섭을 방지하고자 피아노 롤을 사용해서 88개의 주파수들 사이를 옮겨 다니는 방법을 도입함으로써 이 개념을 공고히 하게 되었다.

지난 100년 동안 1차 세계대전 당시 지휘소들 간에 이루어지던 비실시간 저속 통신에서부터 오늘날 항공기, 선박, 지상 시스템 간에 이루어지는 실시간 고속 멀티미디어 통신에 이르기까지 사용되어 온 FH는 군용 애플리케이션에서 새로운 시대에 접어들었다. FH는 블루투스 PAN(Personal Area Network) 같은 무선 개인 통신망과 워키토키, 모형 자동차, 드론 같은 컨수머 및 취미용 무선 분야에도 널리 사용되고 있다.

주파수 호핑이란?

그림 1은 FH의 기본 개념을 보여준다. 전체 주파수 대역과 지속 시간을 2차원 격자로 분할하고 있다. 특정 시간 슬롯에 서로 다른 주파수 서브밴드를 사용해서 통신을 한다. 이렇게 하면, 협대역 간섭에 대한 견고성을 높이고 악의적인 감청이나 재밍에 대한 방어 능력을 높일 수 있는 이점이 있다. 호핑 패턴이 임의적이고 이것을 송신기와 수신기 사이에서만 해독할 수 있으므로, 이를 통해 추가적인 보안 층을 형성하는 것이다.

.jpg)

뿐만 아니라 FH 신호는 상호 간섭을 최소화하므로 기존의 다른 통신들과 대역폭을 쉽게 공유할 수 있어 스펙트럼 효율을 높인다. 호핑 레이트가 더 높아지고 주파수 서브밴드를 더 많이 사용할 수 있게 됨에 따라 더욱 다양해진 많은 애플리케이션에서 FH를 활용할 수 있게 되었다.

차세대 SDR 송수신기

아나로그디바이스(Analog Devices)의 ADRV9002는 듀얼 협대역 및 광대역 SDR 송수신기로서, DPD와 FH 같은 향상된 기능들을 사용해서 보다 뛰어난 RF 성능을 달성한다. ADRV9002는 30MHz ~ 6GHz로 동작하며, 협대역(kHz)과 최대 40MHz에 이르는 광대역 동작으로 극초단파(UHF) 대역, 초단파(VHF) 대역, 산업?과학?의료(ISM) 대역, 셀룰러 주파수 대역을 지원한다.

그림 2는 ADRV9002의 블록 다이어그램이다. 이 디바이스는 송신과 수신 각각에 듀얼 채널과 일련의 첨단 디지털 신호 프로세싱(DSP) 알고리즘을 제공한다. 빨간색 점선으로 표시된 PLL 구조는 매우 독특하다. 다른 많은 송수신기들이 수신 경로와 송신 경로에 각각 하나씩의 전용 PLL을 사용하는 것과 달리, 이 디바이스에는 2개의 RF PLL이 채택되어 있으며 이들 두 PLL은 송신기나 수신기, 또는 둘 다를 지원하거나, 또는 둘 중 어느 것도 지원하지 않는 등 융통성 있게 활용될 수 있다는 점에서 그렇다.

.jpg)

다양한 TDD 애플리케이션에서 송신 전용 모드(1T/2T), 수신 전용 모드(1R/2R), 송신 및 수신 모드(1T1R/2T2R) 같은 단일 채널 및 듀얼 채널 동작으로 FH를 지원하기 위해서는 이러한 유연성이 중요하다. 뿐만 아니라 이 디바이스는 듀얼 채널 동작으로 채널 다이버시티와 채널 다중화를 할 수 있다. 또한 2개의 PLL을 핑퐁 모드로 동작할 수 있으므로 엄격한 FH 타이밍 요건을 수월하게 충족할 수 있다.

ADRV9002의 4가지 주요 FH 기능

2개 PLL 다중화와 고속 PLL 재튜닝으로 극히 빠른 FH 달성

FH를 위해서는 다른 주파수로 전환하기 전에 PLL을 재튜닝해야 한다. ADRV9002는 PLL 활용을 기반으로 다양한 FH 모드를 제공한다2. 그림 1에 보이는 각각의 시간 슬롯이 호핑 프레임에 해당하며, 각각의 호핑 프레임은 그림 3에서 보는 것과 같이 전이 시간(transition time)과 체류 시간(dwell time)으로 이루어진다.

.jpg)

FH 모드가 속도가 느리고 주파수를 전환하는 사이의 전이 시간이 충분히 길 때는(채널 설정 시간과 PLL 튜닝 시간보다 긴 시간) TDD 동작으로 한 쌍의 송신 및 수신 채널을 위해서 하나의 PLL만 필요하다(PLL 재튜닝 모드). 하지만 이 디바이스는 짧은 전이 시간(채널 설정 시간과 PLL 튜닝 시간보다 짧은 시간)으로 빠른 FH를 달성하기 위해서 2개의 PLL을 채택하고 있다(PLL MUX 모드). 2개 PLL이 핑퐁 모드로 번갈아 가면서 동작한다.

즉, 한 PLL이 현재 주파수에 사용되는 동안에 또 다른 PLL을 또 다른 주파수로 튜닝하는 것이다. 그럼으로써 매우 빠른 FH를 가능하게 하고, 다른 주파수로 전환하기 위해서 필요한 전이 시간을 크게 단축할 수 있다. 표 1은 이 두 방식을 요약해서 보여준다.

.jpg)

표 1에서 보듯이, 두 방식 중에서 어떤 것을 선택하느냐는 사용자가 전이 시간을 어떻게 정의하느냐에 따라 달라진다.

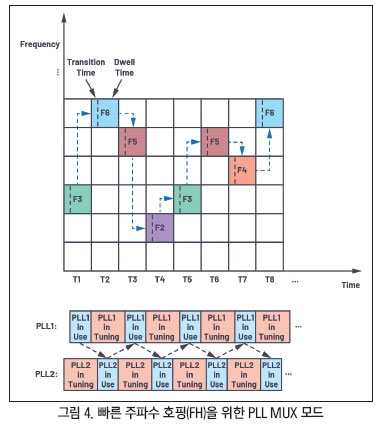

그림 4는 PLL MUX 모드의 컨셉트를 보여준다. 앞서 언급했듯이, 각각의 시간 슬롯이 호핑 프레임에 해당되고, 각각의 호핑 프레임은 전이 시간과 체류 시간으로 이루어진다. 체류 시간에 한 PLL이 사용되는 동안, 다른 PLL은 동일한 호핑 프레임으로 전이 시간이 시작됨과 동시에 튜닝을 시작한다. 그리고 다음 호핑 프레임에서 전이 시간이 끝날 때까지 튜닝을 계속한다. 따라서, PLL MUX 모드가 성공적이기 위해서는 필요한 PLL 튜닝 시간이 한 번의 체류 시간과 두 번의 전이 시간을 합한 것보다 작아야 한다.

PLL MUX 모드를 사용한 FH는 Link 16 같은 군용 애플리케이션에 중요하다. Link 16은 중요한 전술 데이터 링크 표준의 하나로서, 북대서양 조약 기구(NATO)에서 960MHz ~ 1.215GHz의 무선 주파수 대역에서 재밍 방지용 고속 디지털 데이터 링크로서 사용하고 있다. ADRV9002는 초기화 시에 전체적인 호핑 주파수 대역을 적절히 보정함으로써 PLL을 빠르게 튜닝하고 엄격한 타이밍 요건을 충족한다.

PLL 튜닝 시간은 ADRV9002의 PLL 레퍼런스 클럭 속도에 따라서 좌우된다. 표 2는 서로 다른 PLL 레퍼런스 클럭 속도에 따라서 필요한 고속 PLL 튜닝 시간을 보여준다. PLL 레퍼런스 클럭 속도가 300MHz일 때 고속 PLL 튜닝 시간은 약 15μs이다. Link 16은 호핑 프레임 길이가 13μs이므로, 표 1에서 보듯이 전이 시간이 2μs보다 길다면 PLL MUX 모드를 사용할 때 15μs의 PLL 튜닝 시간이 타이밍 요건을 충족할 것이다.

.jpg)

“협대역 간섭이 존재하는 가운데 저속 평탄형 나카가미 페이딩 채널을 통해서 전송된 JTIDS/Link 16 유형 파형의 성능 분석” 논문3에서 기술하고 있듯이, Link 16 메시지 데이터는 패킹 구조에 따라서 단일 펄스나 이중 펄스로 전송할 수 있다. 단일 펄스 구조는 6.4μs 온(on) 시간과 6.6μs 오프(off) 시간으로 이루어지므로 총 지속시간은 13μs이다. 이중 펄스 구조는 2개의 단일 펄스로 이루어지며 동일한 데이터를 서로 다른 캐리어 주파수를 사용해서 전송한다(그림 5). 그러므로 전이 시간이 6.6μs 길이일 수 있는데(>2μs), 이는 ADRV9002를 사용해서 Link 16 FH를 지원할 수 있다.

.jpg)

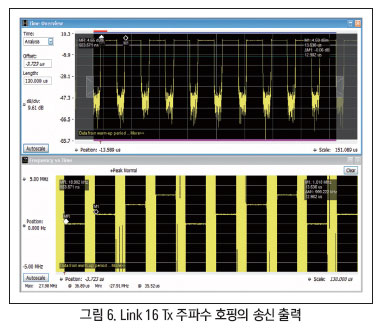

그림 6은 Link 16 유형 호핑 프레임을 사용할 때 ADRV9002의 송신 출력(시간 대비 전력과 시간 대비 주파수)을 보여준다(송신 전용 FH의 경우). ADRV9002를 사용해서 달성 가능한 최소 전이 시간을 보여주기 위해서 여기서는 그림 5의 표준형 Link 16 펄스 구조를 그대로 따르지 않고 온 시간을 6.4μs에서 11μs로 늘리고 오프 시간을 6.6μs에서 2μs로 줄였다. ADRV9002 평가 보드의 송신 출력 포트에 텍트로닉스(Tektronix)의 RSA306B 스펙트럼 분석기를 연결하여 측정했다.

상단 플롯은 시간 대비 전력 성능을 보여준다. 연속적 송신 호핑 프레임들 사이에 약 3μs의 전이 시간으로 매 13μs마다 송신 호핑이 이루어지고 있는 것을 알 수 있다. 하단 플롯은 시간 대비 주파수 성능을 보여준다. 이 측정은 송신 캐리어 주파수를 1MHz 간격으로 4개 주파수를 순환하도록 설정한 것이다. 하단 플롯에서 송신 출력이 1MHz 간격으로 4개 주파수를 순환하는 것을 보면 전체 체류 시간에 걸쳐 주파수 정확도가 우수하다는 것을 알 수 있다.

Link 16 FH의 주파수 정확도를 알아보기 위해서 키사이트(Keysight)의 E5052B와 R&S FSWP 같은 첨단 테스트 장비를 사용해서 추가적인 측정을 실시했다. 표 3의 측정은 송신 캐리어 주파수를 400MHz, 400.1MHz, 400.2MHz, 400.3MHz로 호핑한 것이다. 송신 입력은 모든 호핑 프레임으로 400MHz 출력을 발생하도록 구성했다. 측정 지속시간은 100μs로 설정했다. 이것은 7개 호핑 프레임에 해당한다. 매 128ns 시간 간격으로 주파수를 측정했다.

.jpg)

체류 시간이 시작될 때 PLL이 완벽하게 동기화되는 것으로 확인된다. 체류 시간에 주파수 오차는 위상 잡음 성능에 좌우된다. 표 3에서는 이들 7개 호핑 프레임의 평균, 최대, 최소 주파수 오프셋(출력 주파수와 400MHz의 절대 차이)을 보여준다. 대부분의 프레임에서 평균 주파수 오차가 1ppm 미만이라는 것을 알 수 있다. 수십 번의 측정을 통해 이 결과가 반복적이라는 것을 확인했다. 다만 측정 장비와 테스트 구성에 따른 약간의 차이는 있을 수 있다.

ADRV9002를 사용해서 사용자는 PLL 루프 필터 대역폭을 조절할 수 있다. 표 3의 성능은 PLL 루프 필터 대역폭을 1200kHz로 구성했을 때이다. PLL 필터 대역폭을 넓히면 PLL 재튜닝 시간을 향상시킬 수 있다. 그럼으로써 체류 시간 전에 PLL을 완벽하게 동기화할 수 있다. 루프 필터 대역폭을 선택할 때는 애플리케이션에서 요구되는 위상 잡음 성능도 고려해야 한다.

최대 128개 주파수 항목까지 정적 및 동적 테이블 로드

ADRV9002는 모든 FH 모드에 호핑 테이블 컨셉트를 사용한다2. 호핑 테이블(hop table)은 매 호핑 프레임에 대한 주파수 목록과 그 밖에 다른 동작 파라미터들을 포함한다. 호핑 테이블은 정적으로 로드할 수 있다. 다시 말해, 초기화를 할 때 로드하고 실행 중에는 테이블을 변경할 수 없다는 뜻이다. 호핑 테이블은 동적으로 로드할 수도 있다. 즉, 호핑 중에 호핑 테이블을 로드할 수 있다는 의미이다. 그러므로 실행 중에 사용자가 호핑 테이블의 내용을 변경할 수 있다.

호핑 테이블 역시 핑퐁 방식으로 2개의 서로 다른 테이블을 선택적으로 로드할 수 있으며, 각 호핑 테이블마다 최소 1개에서부터 최대 64개 주파수 항목을 포함할 수 있다. 한 테이블을 현재 호핑 프레임에 사용하는 동안, 다른 테이블을 그 다음 호핑 프레임을 위해 준비시킬 수 있다. 각각의 항목은 특정 호핑 프레임에 사용될 구성을 ADRV9002에게 알려준다.

호핑 테이블은 자동으로 인덱싱하거나(2개의 호핑 테이블을 사용하는 경우, 첫 번째 테이블의 첫 번째 항목에서 시작해서 두 번째 테이블의 마지막 항목까지 간 다음에 다시 첫 번째 테이블의 첫 번째 항목으로 이동. 하나의 호핑 테이블만 사용할 때는 항목들을 계속해서 순환), 혹은 특정 시점에 디지털 GPIO를 통해서 지시된 특정 항목을 언제든 액세스할 수 있다.

.jpg)

그림 7은 각각 N개(1 ≤ N ≤ 64)의 항목을 포함하는 호핑 테이블 A와 B를 사용할 때를 보여준다. 호핑 테이블의 각 항목마다 4개의 파라미터를 포함한다. 호핑 주파수, 중간 주파수(수신 IF 모드), 수신 이득 인덱스, 송신 감쇠가 그것이다. TDD 동작에서는, 사용자가 각각의 호핑 프레임으로 어떤 채널(송신 또는 수신)을 사용할지를 전용 채널 설정 신호(송신 채널용 1개와 수신 채널용 1개)를 사용해서 ADRV9002에 지시해야 한다. 따라서, 호핑 테이블의 각각의 항목은 수신과 송신에 관한 파라미터를 모두 포함하되, 오직 관련 있는 파라미터만 사용된다.

FH에서 호핑 테이블이 어떻게 작동하는지 살펴보기에 앞서, ADRV9002와 베이스밴드 IC(BBIC)가 어떻게 통신하는지 간략히 살펴보자.

.jpg)

그림 8에서 보듯이, BBIC가 FH 동작을 위한 메인으로서 동작하며 FH 모드, 채널 설정 신호(Rx1_ENBALE, Rx2_ENABLE, Tx1_ENABLE, Tx2_ENABLE), HOP 신호(HOP1과 HOP2), 정적 또는 동적 호핑 테이블(호핑 주파수, 수신 IF 주파수, 수신 이득, 송신 감쇠)을 설정한다. BBIC는 SPI 인터페이스나 DGPIO를 통해서 ADRV9002와 통신한다. ADRV9002가 FH 동작을 위한 노드로서 동작하며, BBIC로부터 신호들을 받고 그에 따라서 데이터 경로와 LO를 구성한다.

.jpg)

그림 9에서는 호핑 테이블 A와 B가 각각 1개씩의 주파수만을 포함하고서 동적 테이블 로딩을 하는 것을 보여준다. 이것은 극단적인 경우를 예시한 것으로서, 이 경우에는 사용자가 실행 중에 매 프레임마다 호핑 주파수를 변경할 수 있다. 이 예시에서는 PLL MUX 모드가 사용되고 있다.

그림에서 보듯이, 호핑 신호의 상승 에지와 하강 에지가 호핑 프레임의 타이밍 경계를 정의한다. 앞서 언급했듯이 각각의 호핑 프레임은 전이 시간과 체류 시간으로 이루어진다. 채널 설정 신호의 상승 에지는 호핑 프레임의 유형을 정의하며, 1개의 프레임 지연이 뒤따른다(PLL MUX 모드에는 이 지연이 필요하다).

채널 설정 신호는 송신 설정 신호이거나 수신 설정 신호이다. 그림 9는 이 신호를 단순화해서 보여준다. TDD 동작은 송신과 수신을 모두 수반하므로, 사용자가 송신 설정 신호와 수신 설정 신호를 따로따로 구성해야 한다. 채널 설정 신호는 호핑 프레임 유형을 지시하는 것과 함께 BBIC가 명령한 호핑 테이블 로드를 트리거할 수 있다. 호핑 테이블 로딩은 채널 설정 신호 하강 에지 이후 호핑 신호 에지 전까지는 완료되어야 한다.

그런 다음에는 동일한 호핑 에지에 PLL이 이 주파수로 튜닝하기 시작하고, 그 다음 호핑 에지에 의해 지시되는 다음 번 호핑 프레임을 실행하도록 준비된다. 테이블 A와 테이블 B는 핑퐁 모드로 동작하기 때문에, 로딩이 완료되면 FH는 한편으로 한 테이블의 주파수로 동작하면서 다른 한편으로는 다른 테이블의 주파수로 튜닝한다.

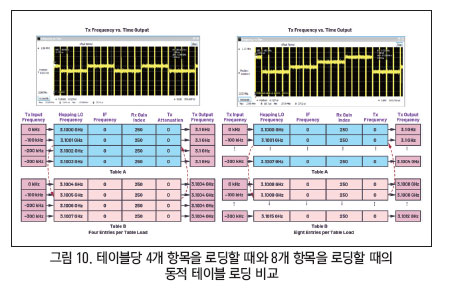

그림 10은 동적 테이블 로딩으로 로드당 4개 항목을 로드할 때와 8개 항목을 로드할 때의 시간 대비 송신 주파수 출력을 나타낸 것이다. 송신 입력은 0kHz, ~100kHz, ~200kHz, ~300kHz 주파수로 4개 프레임이고, 이 프레임들을 계속해서 돌아가며 ADRV9002로 전달한다. 이 경우에도 역시 호핑 프레임과 완벽하게 정렬하고 동기화함으로써, 0kHz 입력 프레임이 3.1GHz LO와 정렬한다. FH 동안, LO가 다음 주파수로 전환하면 송신 입력 주파수 역시 다음 주파수로 전환한다.

FH를 실행하는 동안, 테이블 A와 테이블 B가 동적으로 로딩된다(편의상 테이블의 내용은 로드할 때마다 변경되지 않는 것으로 했다). 테이블당 4개 항목을 로드하는 경우에는, 3.1GHz에서 4개의 연속된 송신 출력 프레임과 3.1004GHz에서 4개의 연속된 프레임이 발생하고, 이 패턴이 계속해서 반복될 것으로 예상할 수 있다.

테이블당 8개 항목을 로드하는 경우에는, 3.1GHz에서 4개의 연속된 송신 출력 프레임, 3.1004GHz에서 4개의 연속 프레임, 3.1008GHz에서 4개의 연속 프레임, 3.1012GHz에서 4개의 연속 프레임이 발생하고, 이 패턴이 계속해서 반복될 것으로 예상할 수 있다. 그림 8의 송신 출력을 보면, 이 동적 테이블 로딩이 우리가 예상한 대로 잘 작동한다는 것을 알 수 있다.

듀얼 채널을 사용한 채널 다이버시티와 채널 다중화

그림 2에서 본 것처럼, ADRV9002는 송신과 수신을 위한 듀얼 채널을 지원한다. 양쪽 채널 모두에 FH를 적용함으로써 채널 다이버시티와 채널 다중화를 달성할 수 있다.

채널 다이버시티는 양쪽 채널이 동일한 PLL(하나 혹은 2개)에 동일한 호핑 테이블과 TDD 타이밍 구성을 사용해서 동시에 호핑하는 것이다. ADRV9002가 제공하는 MCS 기능을 사용하면 동일한 또는 서로 다른 ADRV9002 디바이스 상에서 여러 채널들을 확정적 지연시간으로 완벽하게 동기화할 수 있다. MCS 기능을 사용해서 위상 동기화도 할 수 있다.

그러면 PLL이 주파수를 튜닝할 때마다 위상 동기화가 이루어진다. MCS 기능을 사용해서 FH를 하는 중에도 여러 채널들을 동기화할 수 있으므로, ADRV9002는 FH를 적용한 MIMO 다이버시티 애플리케이션에 사용하기에 매력적인 솔루션을 제공한다.

ADRV9001 시스템 개발 사용자 가이드2에서는 FH를 하면서 MCS를 사용하는 데 필요한 요건들과 한계에 대해서 설명하고 있다.

채널 다중화의 경우에는 각 채널 쌍이 하나의 PLL을 사용하면서 서로 독립적으로 FH를 수행한다. 다만, 매우 빠른 FH를 위해서는 한 쌍의 송신 및 수신 채널에 2개의 PLL이 필요하므로 1개의 ADRV9002 디바이스를 사용할 때는 채널 다중화를 ADI위해 매우 빠른 FH를 적용할 수 없는 한계가 있다.

또 한 가지 주목할 만한 점은, ADRV9002는 FH를 위해 2T2R 모드 외에도 1T2R과 2T1R 동작을 지원하는데, 이는 사용자의 특정한 요구를 충족하도록 유연성을 높인다는 것이다.

FH와 함께 DPD 기능 지원

ADRV9002는 협대역과 광대역 애플리케이션 모두에 DPD 기능을 지원한다. DPD는 전력 증폭기(PA)의 비선형성을 교정함으로써 PA의 효율을 크게 향상시키고 표준에서 정의하는 인접 채널 전력비(ACPR) 요건을 달성하도록 한다.

ADRV9002의 이점 중 하나는 FH에 DPD를 함께 실시할 수 있다는 것이다. 이 경우, 사용자는 최대 8개 주파수 대역을 설정할 수 있으며, DPD 알고리즘이 이들 각각의 주파수 대역에 최적의 솔루션을 생성한다. DPD 솔루션은 일련의 계수들로서, 각각의 대역에서 전송을 끝낼 때는 저장되고 전송을 시작할 때는 로딩된다. 그럼으로써 전체적인 호핑 주파수 대역에 걸쳐서 PA 선형성을 달성하도록 한다.

DPD는 적응형 필터링 프로세스로서 계수 계산을 위해서 일련의 샘플을 일정한 간격으로 포착해야 하므로, 호핑 프레임 길이는 요구되는 DPD 포착 길이를 만족시킬 수 있을 만큼 충분히 길어야 한다. 다만 DPD를 업데이트할 필요 없이 처음에 로딩한 DPD 계수만을 사용하는 경우에는 이 제한이 해당되지 않는다.

ADRV9002의 추적 교정은 통상적으로 고속 FH 동안에는 실행되지 않는다. 하지만 되도록 최상의 성능을 달성하기 위해서, 사용자의 FH 구성에 따라서 여러 주파수 대역에 걸쳐서 초기 교정을 실시할 수 있다.

ADRV9002 송수신기 평가 소프트웨어(TES)를 사용한 FH 성능 평가

평가 보드와 함께 ADRV9002 TES를 사용해서 FH 성능을 평가할 수 있다. TES는 자일링스(Xilinx?) ZC706과 ZCU102 FPGA 보드를 지원한다2. 그림 11에서 보듯이, FH 구성 페이지에서 손쉽게 FH 파라미터를 구성할 수 있다(FH 동작 모드, 호핑 테이블, GPIO 설정, TDD 타이밍 등). 이 TES에는 FPGA 동기화 기능이 내장되어 있으므로, 송신 또는 수신 프레임이 호핑 프레임과 완벽하게 동기화되도록 TDD 타이밍을 세밀하게 제어할 수 있다. 또한 이 TES에는 사용자가 충분히 경험해 볼 수 있도록 많은 FH 예제들을 제공한다.

.jpg)

맺음말

FH는 차세대 SDR 송수신기로서 ADRV9002가 제공하는 향상된 시스템 기능 중의 하나이다. ADRV9002는 2개 PLL을 채택하고, 다양한 FH 모드를 지원하고, 호핑 테이블을 로드하고 인덱싱하는 것을 유연하게 할 수 있으므로 다양한 애플리케이션의 필요를 충족하고 향상된 시스템 성능을 달성하도록 한다. 또한 ADRV9002 TES와 소프트웨어 개발 키트(SDK)를 사용해서 모든 기능들을 꼼꼼하게 평가할 수 있다.

참고문헌

1. John G. Proakis. Digital Communications, 3rd edition. McGraw-Hill, March 1994.

2. UG-1828: ADRV9001 Systen Development User Guide. Analog Devices, Inc., December 2020.

3. Kao Chin-Han. “Performance Analysis of a JTIDS/Link-16-Type Waveform Transmitted over Slow, Flat Nakagami Fading Channels in the Presence of Narrowband Interference.” Naval Postgraduate School, 2008.

저자 소개

미조우 미셸 탄(Mizhou Michelle Tan)은 아나로그디바이스의 제품 애플리케이션 엔지니어이다. RF 송수신기 제품의 설계와 개발을 맡고 있다. 중국 쓰촨 대학에서 전기공학 학사학위 및 석사학위를 취득하고, 2004년에 뉴저지 공과대학에서 전기 및 컴퓨터 공학 박사학위를 취득했다. 2004년부터 2018년까지 아기어 시스템즈(Agere Systens), LSI 로직(LSI Logic), 인텔(Intel)에서 알고리즘, 시스템, 소프트웨어 엔지니어로 재직했다. 기술 컨퍼런스와 저널에 15건 이상의 논문을 발표했으며, 무선 통신 및 디지털 신호 프로세싱과 관련해서 9개 특허를 보유하고 있다.

문의: mizhou.tan@analog.com

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>