최근에 소개된 트랜스 인덕터 전압 레귤레이터(trans-inductor voltage regulator, TLVR)가 CPU, GPU, ASIC 같은 저전압 고전류 부하에 전원을 공급하기 위한 다중 위상 DC-DC 애플리케이션에서 인기가 높아지고 있다. 이 기술이 트랜션트 성능이 뛰어나기 때문이다. 또한 TLVR은 설계와 레이아웃에 유연성을 제공한다. 하지만 TLVR은 몇 가지 단점을 수반한다. 이 글에서는 TLVR 제품 선택이 성능 파라미터에 미치는 영향과 관련한 설계 상의 절충점에 대해서 설명한다.

TLVR 벅 컨버터에서의 전류 리플과 트랜션트

TLVR 벅 컨버터에서의 전류 리플과 트랜션트

다중 위상 벅 컨버터의 성능 향상 관련 소식은 그 내용이 무엇이든 많은 고전류 애플리케이션에서 중요한 관심사이다. 특히 관심이 쏠리는 것은 트랜션트 특성 향상인데, 오늘날 많은 CPU, GPU, ASIC이 매우 엄격한 트랜션트 특성을 요구하기 때문이다. 고효율 역시 에너지 절감과 열 성능을 위해 중요하게 인식된다.

인덕터의 전류 리플은 이 제품의 선택에 영향을 주는 중요한 파라미터이다. 전류 리플은 효율과 출력 전압 리플에 영향을 미칠 뿐만 아니라 트랜션트 성능, 솔루션 크기, 그 밖에 다른 성능 지표들과도 간접적으로 연관이 있다. 또 다른 중요한 특성은 트랜션트 시의 전류 슬루율이다. 슬루율은 트랜션트 성능에 있어서 근본적인 제약 요인이다. 대개의 경우, 전류 리플(그러므로 효율)과 트랜션트 성능(출력 커패시턴스 양 등에 직접적으로 영향을 미침)은 설계 결정에 있어서 절충 관계에 있다.

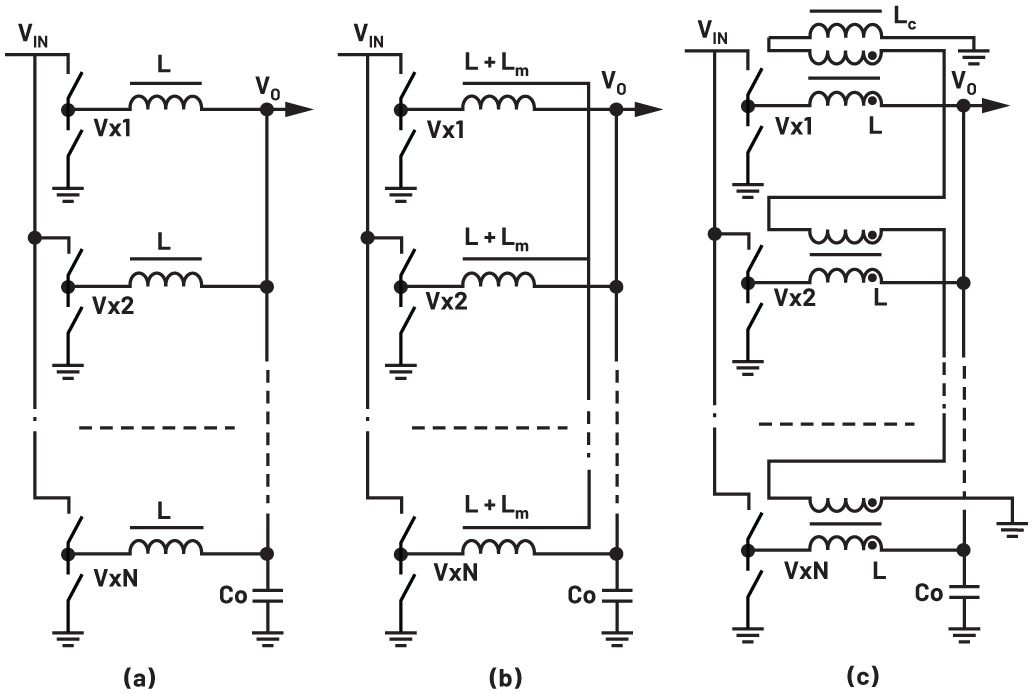

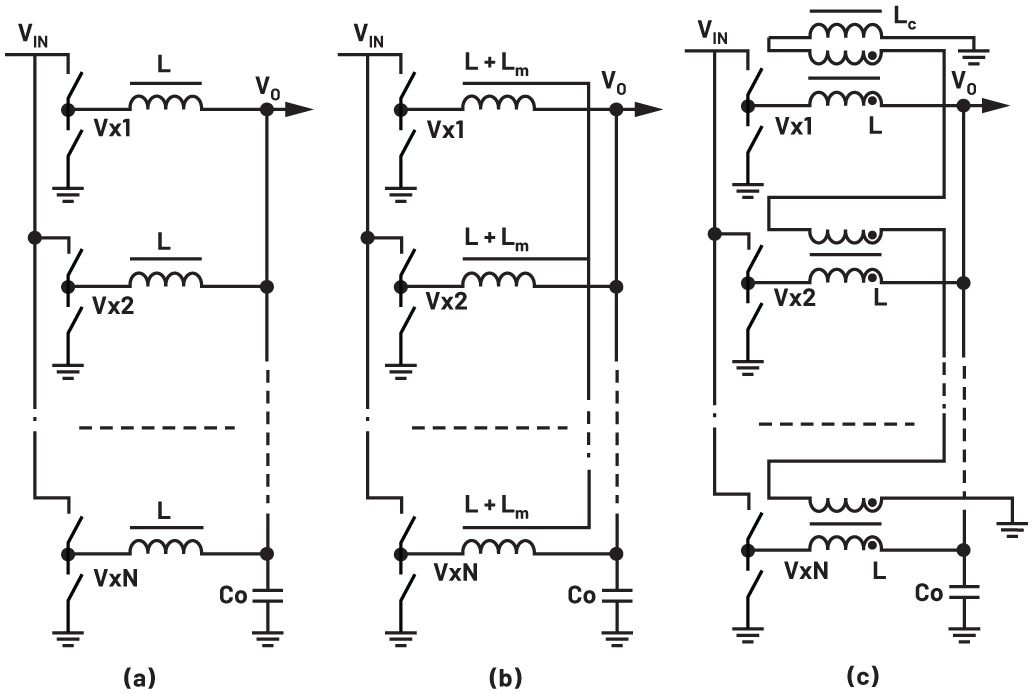

그림 1a는 디스크리트 인덕터(DL)를 사용하는 전통적인 다중 위상 벅 컨버터를 보여준다. 이 설계는 모든 위상들 간에 적절한 위상 차이를 사용해서 파형들을 적절히 인터리브한다. 또 다른 방법으로서 DL 대신 결합 인덕터(CL)를 사용할 수도 있다(

그림 1b)

1-3,5. 그림 1c는 TLVR이라고 하는 또 다른 대안을 보여주는데, 여기서 튜닝 인덕터(Lc)는 전류 리플과 트랜션트 두 가지 모두에 영향을 미친다

4,6,7,10.

그림 1. (a) 디스크리트 인덕터(DL), (b) 결합 인덕터(CL), (c) TLVR을 사용한 다중 위상 벅 컨버터

TLVR의 기본 개념은 디스크리트 인덕터에 이차 권선을 추가하고 이차 권선들을 전기적으로 연결해서 위상들을 연동하는 것이다. 그러므로 개념적으로는 결합 인덕터와 유사하다. 연동된 모든 위상들 사이에 AC 파형을 애버리징하여 특정한 트랜션트 슬루율로 더 나은 전류 리플을 달성하는 것이다.

하지만 TLVR은 최대 위상 전류 정격 때문에 유효 결합 인덕턴스가 제한적이다. 이러한 한계점은, TLVR 트랜스포머가 전류의 DC 성분을 통과시키지 않고 그러므로 자기 결합 인덕터에서 그러하듯 위상들 간에 DC 성분이 제거되지 않는다는 사실로부터 비롯되는 것이다. 이 글에서는 TLVR의 성능 파라미터들과 특정한 설계 절충에 대해서 설명한다.

TLVR의 리플과 전류 슬루율에 관한 수학적 모델을 처음으로 제시한 것은 아마도 참고문헌 [7]에서일 것이다. 이 모델은 어느 회로 조건(듀티 사이클 D = V

o/V

IN, 위상 수 N

ph 등)에나 적용할 수 있는 매우 유용한 모델이기는 하지만, 몇 가지 제약을 가지고 있다. 예를 들어 L

c 값(

그림 1c에서 튜닝 인덕터)이 낮으면 오차를 증가시킴으로써 L

c = 0일 때는 무한대가 된다. L

c = 개방일 때보다 낮은 L

c 값일 때의 코너 사례가 더 중요하다. TLVR을 사용하는 가장 큰 이유가 트랜션트 향상에 있고, 이는 적당히 낮은 L

c 값을 의미하기 때문이다.

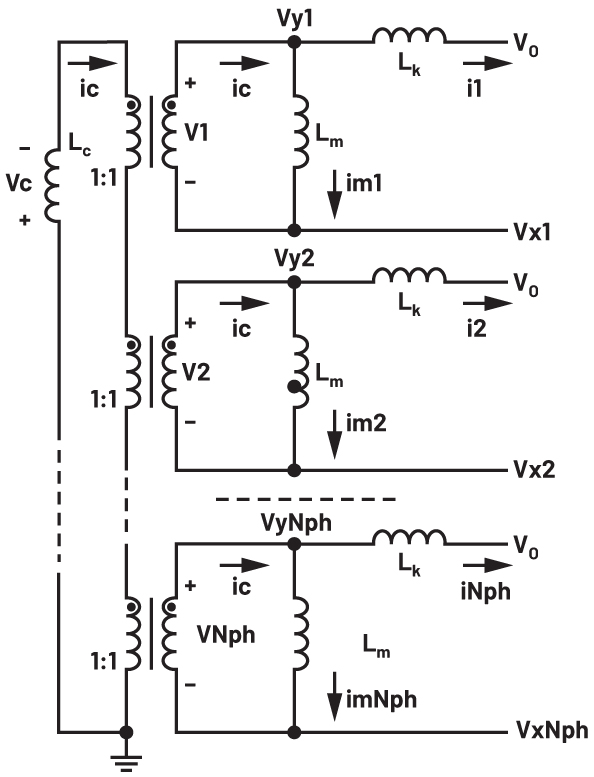

이에 좀더 정확한 TLVR 공식을 도출했는데, 이 공식에 해당 V

x 상태를 대입하면 정상 상태(전류 리플 관련) 또는 트랜션트 시의 전류 슬루율을 구할 수 있다

10. 그럼으로써 보다 정확한 등가 TLVR 회로를 도출할 수 있다(

그림 2). 이 모델은 어떠한 코너 사례에서든 시뮬레이션과 상관성이 극히 우수한데, 정상 상태(steady state) 시에 전류 슬루율이 D < 1/N

ph인 경우에만 유효하다. 이것이 허용되는 이유는 TLVR이 정확히 D < 1/N

ph 영역에 대해 DL 베이스라인으로부터 최대의 전류 리플 증가를 가지며 N

ph가 충분히 높을 때 DL 리플에 근접하는 것으로 나타나기 때문이다

9,10.

그림 2. TLVR 모델10

통상적으로 TLVR 값은 데이터 시트에 디스크리트 인덕터 DL과 같은 방식으로 표기되는데, 이로부터 TLVR을 도출할 수 있다. 그림 2의 모델에서 TLVR 총 값, 다시 말해 자체 인덕턴스는 소량의 L

k와 그 나머지로 나뉘어지며, 이 나머지가 TLVR 트랜스포머의 상호 인덕턴스가 되므로 L

m = TLVR - L

k이다(

식 1).

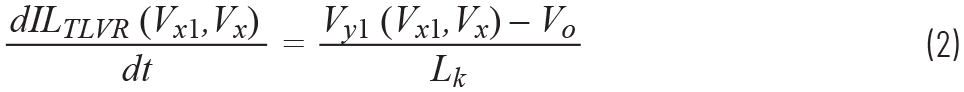

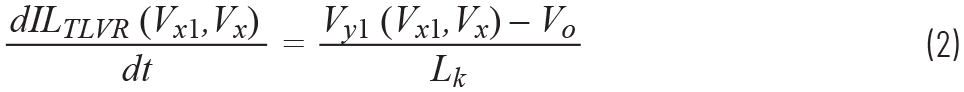

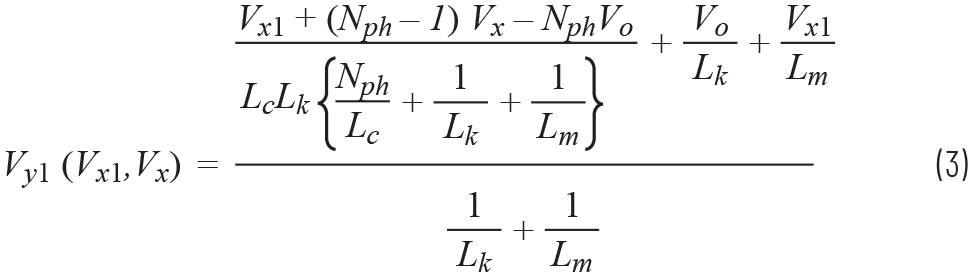

그림 2의 모델에 근거해서, TLVR의 전류 슬루율은

공식 2와 같이 나타낼 수 있다. 이 공식에서 L

k는 메인 권선과 보조 권선 사이의 TLVR 누설이다. V

x1 전압을 해당 위상에 대입하고 나머지 모든 V

x 노드는 동일한 전압인 것으로 간주한다(V

IN 또는 0). 해당 노드 전압 V

y1은 공식 3에서 구할 수 있다. 공식 2를 사용해서 TLVR의 최대 트랜션트 슬루율을 바로 계산할 수 있다. V

x1 = V

x로 하고 이들 전압을 V

IN(상승) 또는 0(하강)으로 지정한다.

마찬가지로

공식 2의 전류 슬루율을 적용해서

공식 4로 정상 상태 리플을 계산할 수 있다. 이 공식에서 V

x1 = V

IN이고 다른 모든 스위칭 노드들은 V

x = 0이다. 다만 공식 4는 D < 1/N

ph에 대해서만 유효한데, 전체적인 턴온 시간 D/Fs에 대해 단일의 동일한 슬루율인 것으로 간주하기 때문이다.

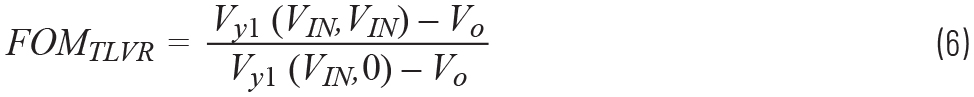

위에서 보듯이, FOM(figure-of-merit)은 시스템 성능을 나타내는 아주 좋은 지표이고, 대개는 FOM을 극대화하는 것이 최적의 절충을 이루는 좋은 방법이다

9,10. 하지만 높은 FOM만으로는 특정 애플리케이션에서 모든 파라미터가 만족스러울 것이라고 보장할 수 없다. 높은 FOM은 좋은 설계라는 것을 알려줄 뿐이다. FOM은

공식 5와 같이 정의할 수 있는데, 이 공식은 D < 1/N

ph에 사용하기에 적합하다. 그러므로 TLVR의 FOM은

공식 6과 같이 표현할 수 있다.

비교를 위해 CL 공식을 사용하는데(여기서는 표시하지 않음), 핵심은 TLVR의 성능과 설계 절충이다

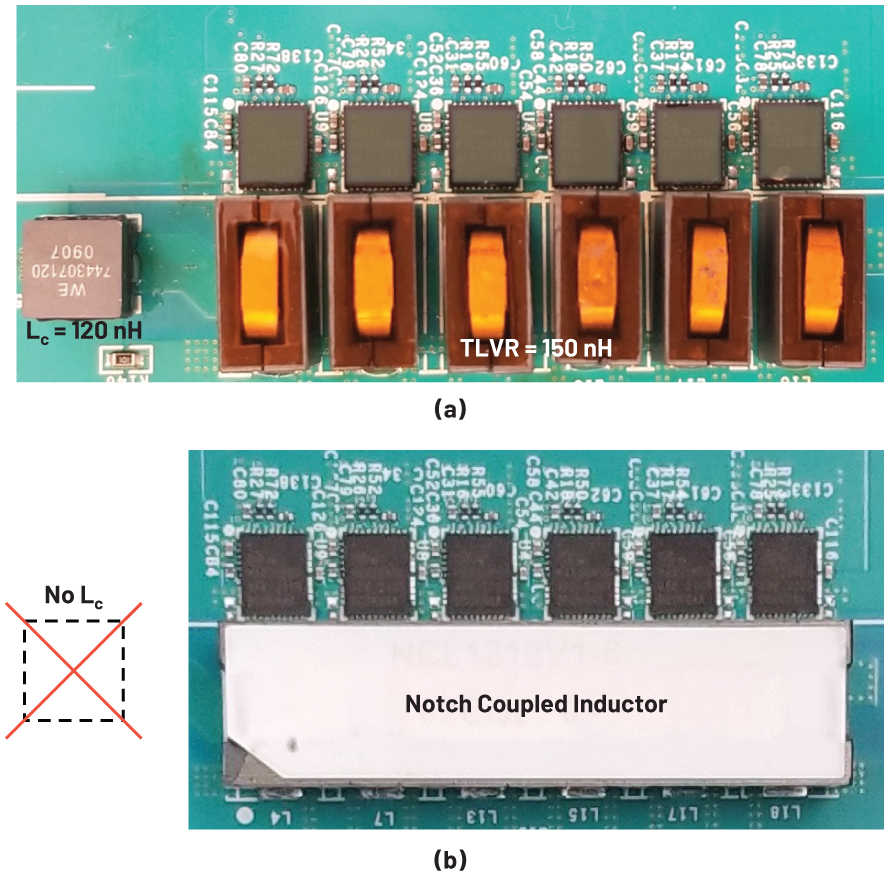

5,10. 노치 결합 인덕터(NCL) 구조 또한 비교를 위한 벤치마크로 사용한다. 동일한 풋프린트 및 크기로 TLVR = 150nH 솔루션과 비교한다10.

TLVR의 설계 절충

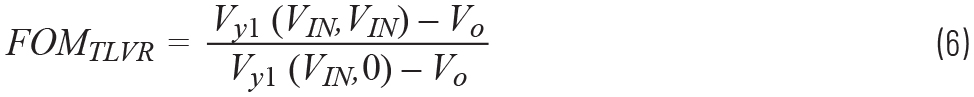

TLVR의 주요 성능 파라미터는 튜닝 인덕터(L

c)의 함수로서

그림 3에서 확인할 수 있는데, 이는 12V 대 1.8V 6위상 설계(전류 리플을 위해 Fs = 300kHz)를 기반으로 한다. TLVR = 150nH는 주어진 크기에서 I

sat/ph 사양을 가까스로 충족하고, 그럼으로써 TLVR 리플을 최소화하고 효율을 극대화하기 위해 가능한 최대 값이다. TLVR = 150nH와 비교를 위한 베이스라인으로서 DL = 150nH와 NCL = 6x 25nH(L

m = 375nH)도 표시하고 있다. 또한 그림 3의 모든 TLVR 곡선 상에 실제 설계 포인트인 L

c = 120nH를 표시하고 있다.

그림 3은 가로 축에서 L

c에 따른 (a) FOM, (b) 전류 트랜션트 슬루율, (c) 전류 리플을 보여준다. L

c가 높아질수록 모든 TLVR 곡선이 DL 성능에 점근적으로 가까워진다는 것을 알 수 있다. TLVR의 FOM은 Lc 값이 낮아질수록 높아지는데, 이는 트랜션트 슬루율이 꽤 높아지기 때문이다. 대신에, 이미 리플이 상당히 높은 DL 베이스라인보다도 전류 리플이 좀더 높다(그림 3c). TLVR FOM은 애초의 DL에 절연 기능을 갖춘 이차 권선을 추가했을 때 페라이트가 감소하는 것을 반영하지 않고 그려진 것이다. 예상대로, TLVR의 리플이 DL 베이스라인보다 항상 더 높다는 것을 알 수 있다

8-10.

그림 3. Lc에 따른 TLVR의 절충. (a) FOM, (b) 전류 슬루율(상승), (c) 전류 리플. 실제 설계 포인트 Lc = 120nH도 표시하고 있다. (12V 대 1.8V, 6위상, Fs = 300kHz)

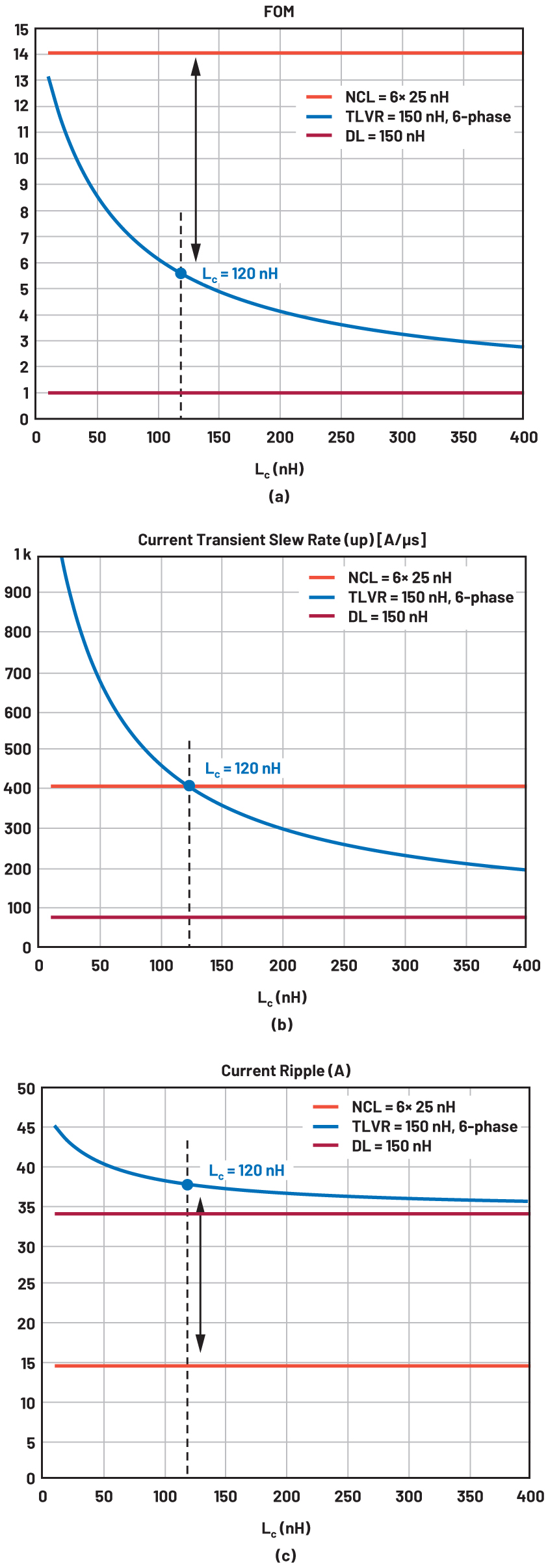

그림 4는 TLVR 값(유효 L

m)에 따른 FOM, 트랜션트 슬루율, 전류 리플의 함수를 보여준다. 다만, 이들 수학적 곡선들에서, TLVR의 Isat 사양은 위상당 최대 I

sat이고(테스트 솔루션에서 TLVR = 150nH일 때 I

sat = 65A), NCL의 Lm에 대한 I

sat은 훨씬 더 낮다(L

m = 375nH일 때 보수적으로 I

sat = 25A, 이는 위상들 간의 전류 불균형을 견디기 위해서다).

그러므로 테스트 솔루션의 동일한 주어진 크기에서, TLVR 곡선은 150nH 이후, NCL 곡선은 375nH 이후가 이론적인 값이다(이들 값을 확장하기 위해서는 더 큰 크기가 필요할 것이다). TLVR과 CL은 전기 모델이 비슷하고 L

m의 함수로서 관련 곡선이 서로 비슷한데, 요점은 주어진 체적에서의 상호 인덕턴스가 TLVR과 CL이 매우 다르게 항상 제한적이라는 것이다

10. 이와 같은 방법으로 실제적 관점에서 동일한 체적으로 TLVR과 NCL을 비교했다.

그림 4. TLVR 값(Lm) 대 TLVR 절충: (a) FOM, (b) 전류 슬루율(상승), (c) 전류 리플. Lc = 120nH로 주어진 크기에서 최대 값인 TLVR = 150nH 및 Lm = 375nH(NCL)를 표시하고 있다. (12V 대 1.8V, 6위상, Fs = 300kHz)

예상대로 TLVR과 NCL 모두 L

m이 증가함에 따라서 결합 계수와 FOM이 높아진다(그림 4a)

10. 트랜션트 슬루율은 대체로 NCL은 누설 인덕턴스(L

k), TLVR은 튜닝 인덕터(L

c)에 의해 좌우되므로(L

m이 아니라),

그림 4b의 곡선들이 거의 평평하다. 다만, TLVR 값(실제로는 L

m)이 매우 작을 때는, 실제적으로 병렬로 L

c를 단락시키기 시작하고 트랜션트 슬루율이 급격하게 높아진다.

그림 4c에서는 TLVR과 NCL 모두 L

m을 높이는 것이 전류 리플을 낮추기 위해 매우 유리하다는 것을 알 수 있다(그림 4b에서 알 수 있듯이, L

m을 높인다고 해서 트랜션트가 악화되지는 않는다). L

m의 함수로서 TLVR과 NCL의 전류 리플 곡선이 매우 비슷한데, 이는 이 둘의 전기적 모델이 비슷하다는 점에서 예상 가능한 것이지만 Lm 값의 한계는 크게 다르다

10. 물론 이 차이는 대부분이 주어진 크기에서 L

m에 요구되는 Isat 정격으로부터 비롯되므로, NCL이 TLVR보다 훨씬 더 작은 전류 리플을 갖는다.

시험 결과

시험을 위해 NCL을 TLVR과 동일한 풋프린트로 TLVR 솔루션의 모든 외관상 규격과 일치하도록 설계했다

10.

그림 5는 동일한 보드 상에 설계된 두 가지 테스트 솔루션을 보여준다(NCL은 L

c가 필요하지 않다).

그림 5. 동일한 보드 상에 설계된 두 가지 테스트 솔루션. (a) TLVR, (b) NCL

슬루율 수치(그림 3b와 그림 4b)에서 예상할 수 있듯이, TLVR과 NCL 둘 다 매우 빠른 솔루션이다. 의도적으로 두 솔루션이 동일한 트랜션트 성능이 되도록 검증했는데, F

s를 300kHz로 낮추더라도 위상들을 서로 결합한 6위상 솔루션에서 피드백 대역폭 제한을 일으키지 않았다

8.

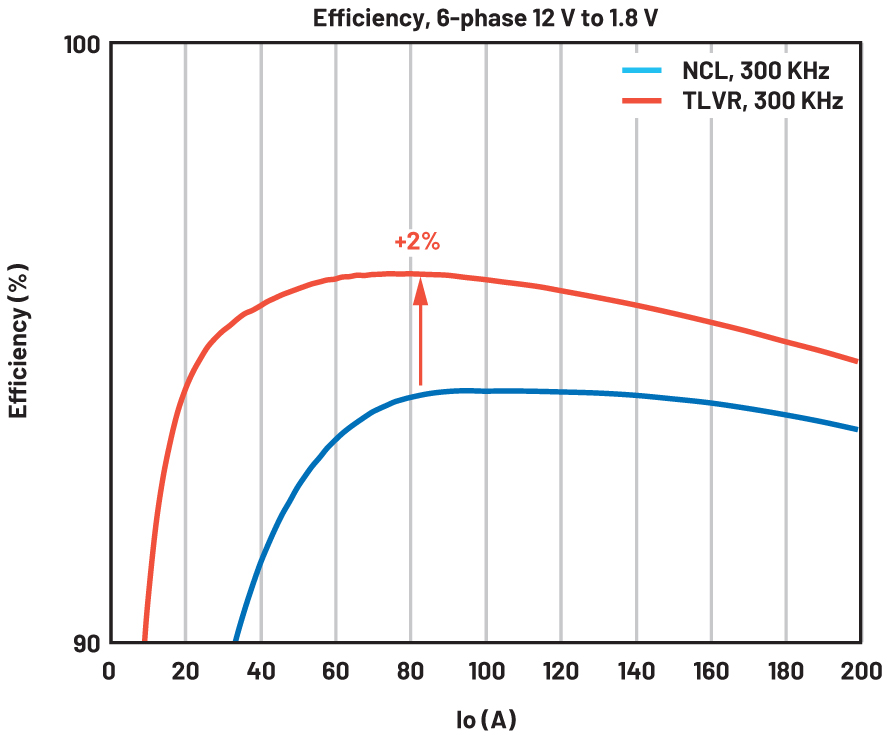

NCL이 TLVR보다 FOM이 훨씬 더 높기 때문에(그림 3a) 트랜션트 성능을 같게 한 결과, NCL은 최대 2.6배 더 낮은 전류 리플을 갖게 되었다.

그림 6은 결과 효율을 비교해서 보여주는데, TLVR 성능은 피크-대-피크 전류 리플이 큰 것으로 나타난다.

그림 6. 동일한 보드 상에서 TLVR과 NCL의 Io에 따른 효율 비교. (6위상, 12V 대 1.8V 설계)

CL 특히 NCL의 누설은 TLVR 값보다 통상적으로 훨씬 낮기 때문에, 위상당 전류 용량 역시 CL과 NCL이 훨씬 더 높다. TLVR = 150nH 사례에서 I

sat = 65A(위상당)이고, 동일한 체적에서 NCL = 6x 25nH는 I

sat이 위상당 300A 이상인 것으로 나타났다.

맺음말

TLVR은 대체로 FOM이 2에 이르므로, FOM = 1인 디스크리트 인덕터를 기준으로 했을 때 성능이 향상된 것으로 볼 수 있다. 이는 TLVR이 전류 리플이 증가하는 것에 비해서 더 빠른 비율로 트랜션트 성능을 향상시키기 때문이다. 하지만 TLVR은 트랜션트를 향상시키는 대신 몇 가지 단점을 수반한다.

예를 들어 TLVR은 낮은 유효 자화 인덕턴스와 L

c로 위상들을 연동하기 때문에 동일한 값일 때 DL보다 전류 리플이 항상 더 높다. 이는 효율에 부정적인 영향을 미치며, 특히 고전압 절연 기능을 갖춘 이차 권선을 추가할 때 페라이트 단면이 감소하는 것과 관련해서 그렇다(원래의 DL과 동일한 I

sat이라고 했을 때). 이 글에서는 페라이트 손실로 인해 추가적인 인덕턴스 값 손실이 발생되는 것에 관해서는 고려하지 않았다. 직렬로 연결되는 이차 TLVR 권선은 잠재적인 고전압 관련 우려를 낳을 수 있고, 이 때문에 자기 소자 비용이 증가할 수 있다

8.

TLVR의 트랜션트 전류 슬루율은 통상적으로 L

c에 의해서 결정되나, Lm이 충분히 낮으면 L

m이 실제적으로 L

c를 단락시킴으로써 더 빠른 트랜션트를 달성할 수 있다. 다만 반대급부로서 전류 리플이 아주 커짐으로써 효율에 부정적인 영향을 미친다.

대체로 TLVR은 결합 인덕터와 비슷하게 동작한다. 다만 TLVR은 최대 전류 정격이 유효 L

m을 제한하고 성능을 제대로 발휘하지 못하도록 할 수 있다. 동일한 체적일 때, CL 또는 NCL은 통상적으로 몇 배 높은 L

m에 의해서 훨씬 더 높은 FOM과 그러므로 더 높은 성능을 달성할 수 있다.

결론적으로, 이 글에서 살펴본 사례에서는 NCL이 효율이 훨씬 더 우수한 것으로 나타난다. 반면, TLVR은 트랜션트 성능을 약간 향상하며

10, 그러면서 비용에 영향을 미치거나 고전압과 관련한 우려를 낳지는 않는다.

부가적으로, 위상당 I

sat 전류 용량에 있어서는 NCL이 TLVR에 비해 훨씬 유리하다(이 글에서 설명한 사례에서는 4.5배 이상의 차이).

참고문헌

1 Aaron M. Schultz and Charles R. Sullivan. “Voltage Converter with Coupled Inductive Windings, and Associated Methods.” U.S. Patent 6,362,986, March 2001.

2 Jieli Li. “Coupled Inductor Design in DC-to-DC Converters.” M.S. thesis, 2001, Dartmouth College.

3 Pit-Leong Wong, Peng Xu, P. Yang, and Fred C. Lee. “Performance Improvements of Interleaving VRMs with Coupling Inductors.” IEEE Transactions on Power Electronics, vol. 16, no. 4, July 2001.

4 Ming Xu, Yucheng Ying, Qiang Li, and Fred C. Lee. “Novel Coupled-Inductor Multi-phase VRs.” IEEE, 2007.

5 Alexandr Ikriannikov. “Coupled Inductor Basics and Benefits.” Analog Devices, 2021.

6 S. Jiang, X. Li, M. Yazdani, and C. Chung. “Driving 48 V Technology Innovations Forward?Hybrid Converters and Trans-inductor Voltage Regulator (TLVR).” IEEE, 2020.

7 “Multiphase Buck Converter with TLVR Output Filter.” Infineon Technologies, February, 2021.

8 Alexandr Ikriannikov. “TLVR High Voltage Considerations.” Power Systems Design, 2021.

9 Alexandr Ikriannikov. “Evolution and Comparison of Magnetics for the Multiphase DC-DC Applications.” IEEE, March 2023.

10 Alexandr Ikriannikov and Di Yao. “Converters with Multiphase Magnetics: TLVR vs CL and the Novel Optimized Structure.” PCIM Europe, May 2023.

저자 소개

알렉산드르 이크리안니코프(Alexandr Ikriannikov)는 아나로그디바이스(Analog Devices)의 통신 및 클라우드 사업부 펠로우이다. 2000년에 캘리포니아 공대에서 전기공학 박사학위를 취득했으며, Cuk 박사의 지도 하에 전력 전자공학을 전공했다. 대학원에서 AC-DC 애플리케이션 용의 PFC와 화성 탐사선용 15V 대 400V DC-DC 같은 프로젝트들을 수행했다.

대학원 졸업 후에는 파워 텐(Power Ten)에 입사해서 수 kW 대의 AC-DC 전원장치 재설계 및 최적화를 맡았으며, 2001년에는 볼테라 세미컨덕터(Volterra Semiconductor)로 옮겨서 저전압 고전류 애플리케이션과 결합 인덕터를 담당했다. (볼테라를 2013년에 맥심 인터그레이티드(Maxim Integrated)가 인수했고, 이후 맥심을 아나로그디바이스가 인수했다) 현재 IEEE의 시니어 회원이다. 70개 이상의 미국 특허를 보유하고 다수의 특허를 출원 중이며, 전력 전자공학과 관련한 여러 편의 문헌을 저작했다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>